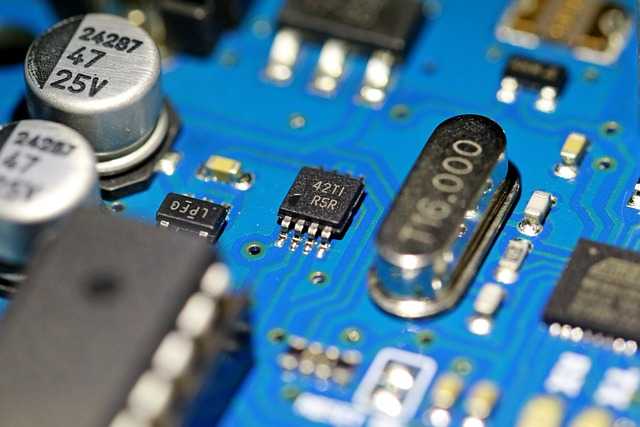

반도체 산업의 핵심 경쟁력은 바로 ‘회로 집적도’입니다. 더 작은 면적에 더 많은 트랜지스터를 집적할수록, 성능은 향상되고 전력 소모는 줄어들며, 비용 또한 절감됩니다. 이 글에서는 회로 집적도 향상을 위한 혁신적인 기술과 공정 연구의 최전선을 살펴보고, 미래 반도체 기술의 발전 방향을 예측해 보겠습니다.

1. 회로 집적도 향상: 왜 중요한가요?

회로 집적도는 반도체 성능을 좌우하는 가장 중요한 요소 중 하나입니다. 집적도가 높아질수록 더 많은 기능을 담을 수 있고, 처리 속도는 빨라지며, 전력 효율도 높아집니다. 스마트폰의 강력한 성능부터 인공지능(AI)의 발전까지, 모든 것은 더 높은 회로 집적도에 기반하고 있습니다. 집적도 향상은 단순히 기술의 발전을 넘어, 더 빠르고, 더 효율적이며, 더 지능적인 미래 사회를 구축하는 데 필수적인 요소입니다. 이는 곧 경제적, 사회적 이점으로 이어지며, 각종 산업의 혁신을 주도하는 핵심 동력이 됩니다. 높은 집적도는 더 작고 가벼운 기기를 만들 수 있게 하며, 소형화는 휴대성을 높여 편의성을 증대시킵니다. 또한, 고성능 저전력 시스템을 구현하여 배터리 수명을 연장하는 등 에너지 효율 향상에도 크게 기여합니다.

2. 회로 집적도 향상 기술: 미세화 공정의 진화

회로 집적도 향상의 핵심은 바로 미세화 공정입니다. 수십 년간 반도체 업계는 꾸준히 트랜지스터의 크기를 줄이는 데 집중해 왔습니다. 이를 위해 다음과 같은 혁신적인 기술들이 개발되어 적용되고 있습니다.

| 기술 | 설명 | 장점 | 단점 |

|---|---|---|---|

| EUV 리소그래피 | 극자외선을 이용한 미세 패턴 제작 기술 | 초미세 패턴 구현 가능 | 고가의 장비 및 높은 기술 장벽 |

| 다층 배선 기술 | 여러 층의 배선을 통해 회로 간 연결 효율 증가 | 회로 간 간섭 감소, 전송 속도 향상 | 공정 복잡성 증가 |

| 3D 적층 기술 | 칩을 수직으로 쌓아 집적도 향상 | 면적 효율 증대, 성능 향상 | 열 관리 및 신호 전달 문제 |

| FinFET 및 GAAFET | 트랜지스터 구조 혁신을 통해 누설 전류 감소 및 성능 향상 | 전력 효율 증대, 고성능 구현 | 복잡한 제조 공정 |

| 새로운 재료 도입 | 실리콘보다 우수한 특성을 가진 신소재 (예: 탄소 나노튜브, 그래핀) 활용 | 더 높은 성능과 효율 | 재료 합성 및 공정 기술의 어려움 |

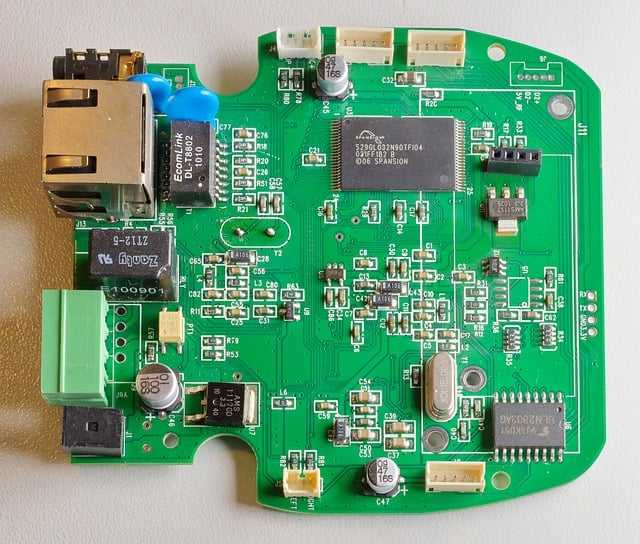

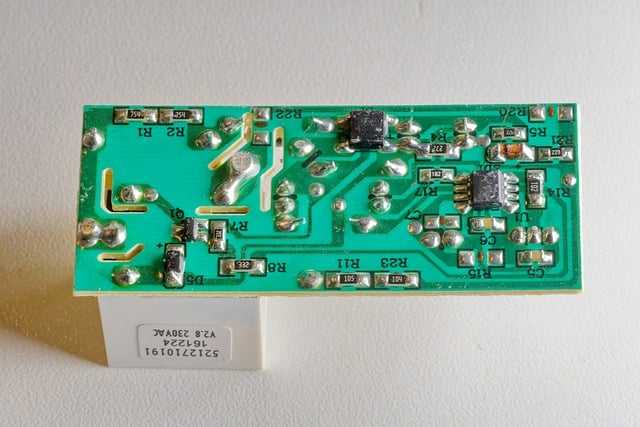

3. 첨단 패키징 기술: 집적도의 새로운 지평

미세화 공정의 한계에 직면하면서, 첨단 패키징 기술이 주목받고 있습니다. 여러 개의 칩을 하나로 묶거나, 기판 위에 다양한 기능을 통합하는 기술을 통해 회로 집적도를 높일 수 있습니다. 대표적인 기술로는 시스템 인 패키지(SiP), 3D 패키징 등이 있으며, 이러한 기술들은 미래 반도체 기술 발전에 중요한 역할을 할 것으로 예상됩니다. 특히, Heterogeneous Integration (이종 집적) 기술은 서로 다른 반도체 기술을 하나의 패키지에 통합함으로써, 기능성과 성능을 극대화하는 데 큰 기여를 하고 있습니다.

4. 회로 집적도 향상을 위한 미래 연구 방향

미래의 회로 집적도 향상을 위한 연구는 더욱 혁신적인 기술과 접근 방식을 요구합니다. 예를 들어, 양자 컴퓨팅, 뉴로모픽 컴퓨팅 등의 새로운 컴퓨팅 패러다임은 기존의 집적도 향상 방식과는 다른 접근법을 필요로 합니다. 또한, 인공지능(AI)을 활용한 설계 자동화 기술은 더욱 복잡해지는 반도체 설계 과정을 효율적으로 관리하는 데 중요한 역할을 할 것입니다. 지속적인 연구개발을 통해 더욱 높은 집적도를 구현하고, 반도체 기술의 한계를 뛰어넘는 혁신을 이루어낼 수 있을 것입니다. 🌱

함께 보면 좋은 정보: 관련 키워드 정보

1. EUV 리소그래피

EUV 리소그래피는 극자외선(13.5nm 파장)을 이용하여 반도체 웨이퍼에 미세한 회로 패턴을 새기는 기술입니다. 기존의 ArF 리소그래피보다 훨씬 작은 패턴을 구현할 수 있어, 회로 집적도 향상에 필수적인 기술로 평가받고 있습니다. 그러나, 고가의 장비와 높은 기술 장벽으로 인해 일부 대기업만이 EUV 장비를 보유하고 있습니다.

2. 3D 적층 기술 (3D Stacking)

3D 적층 기술은 여러 개의 칩을 수직으로 쌓아 하나의 패키지로 만드는 기술입니다. 이를 통해 기존의 2차원 집적 방식보다 훨씬 높은 집적도를 달성할 수 있으며, 성능 향상과 전력 소모 감소에도 효과적입니다. TSV (Through Silicon Via) 기술 등이 3D 적층 기술의 핵심 요소입니다.

3. FinFET 및 GAAFET 트랜지스터

FinFET (Fin Field-Effect Transistor)와 GAAFET (Gate-All-Around Field-Effect Transistor)는 기존의 평면형 트랜지스터 구조를 벗어나, 트랜지스터의 게이트를 3차원으로 감싸는 구조를 가지고 있습니다. 이를 통해 누설 전류를 감소시키고 성능을 향상시킬 수 있습니다. GAAFET은 FinFET보다 더욱 미세한 공정에 적합한 차세대 트랜지스터 기술로 주목받고 있습니다.